- 您现在的位置:买卖IC网 > Sheet目录479 > MRF49XAT-I/ST (Microchip Technology)IC RF TXRX 433/868/915 16-TSSOP

MRF49XA

APPENDIX A:

READ SEQUENCE

AND PACKET

STRUCTURES

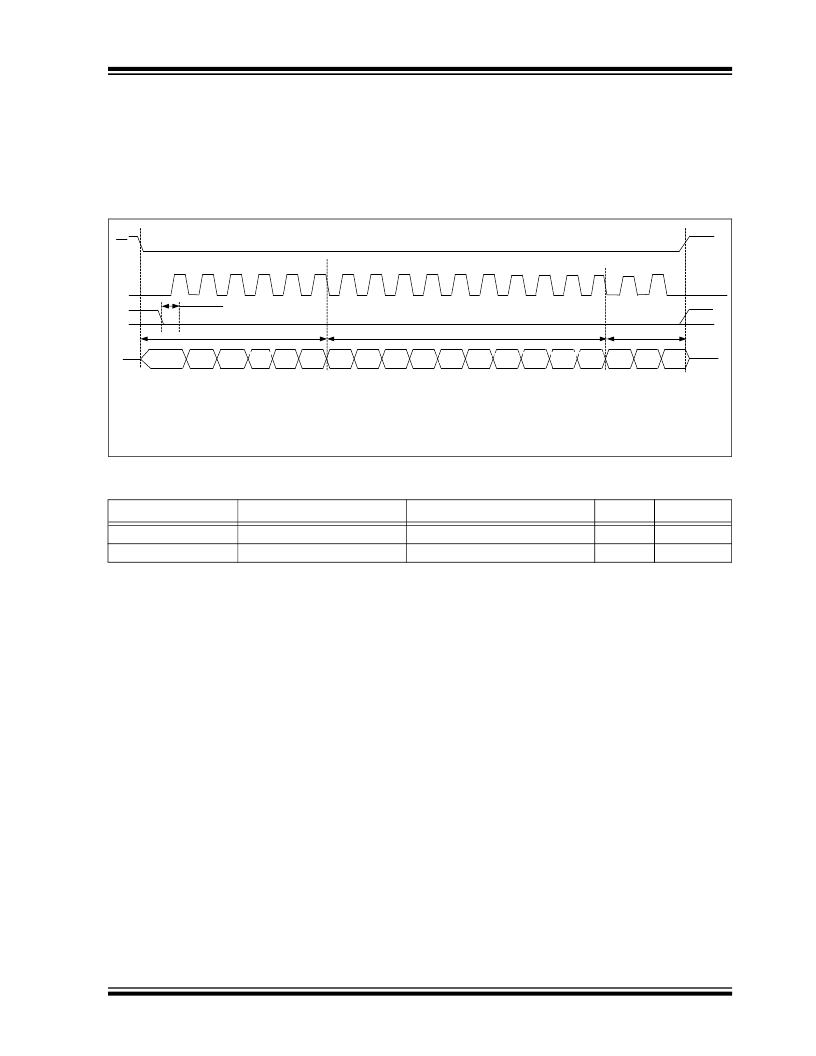

Figure 1 shows the STSREG read sequence with FIFO

read as an example.

FIGURE A-1:

CS

STSREG READ SEQUENCE

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

SCK

Command

SDI

Interrupt Bits Out

Status Bits Out

FIFO Out

(1)(2)(3)

(1,2,3)

(1,2,3)

SDO

TXRXFIFO

POR

TXOWR

XOF

WUTI

NT

LCE

XINT

LBTD

FIFO

EM

ATRS

SI

DQDO

CLKRL

AFCCT

OFFSV

OFFSB

<3>

OFFSB

<2>

OFFSB

<1>

OFFSB

<0>

FO

FO+1

FO+2

(Latched) (Latched) (Latched) (Latched) (Latched)

(Sign)

Note: 1. Applicable when the RXCEN bit is set using the PMCREG.

2. Applicable when the RXCEN bit is cleared using the PMCREG.

3. These bits are internally latched and the other bits are only multiplexed out.

TABLE A-1:

RECOMMENDED FIFO PACKET STRUCTURES

Length

Minimum Length

Preamble

4-8 bits (0x0A or 0x05)

Synchronous Word/Network ID

0xD4 (programmable)

Payload

—

CRC

4-bit-1 byte

Recommended Length 8-12 bits (e.g., 0xAA or 0x55)

0x2DD4 (D4 is programmable)

—

2 bytes

? 2009-2011 Microchip Technology Inc.

Preliminary

DS70590C-page 93

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MRF89XA-I/MQ

TXRX ISM SUB-GHZ ULP 32QFN

MRF89XAM9A-I/RM

IC TXRX MOD 915MHZ ULP SUB-GHZ

MRX-001-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002SL-433DR-B

MODULE RCVR 433MHZ SAW LN 24DIP

MRX-005-915DR-B

MODULE RECEIVER 915MHZ 18DIP

MRX-005SL-915DR-B

MODULE RCVR 915MHZ SAW LN 24DIP

MRX-007-433DR-B

MODULE RECEIVER 433MHZ 18DIP

相关代理商/技术参数

MRF49XAT-I/T

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF49XAT-I-ST

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF49XAT-I-T

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF4A(AMMO)

制造商:Bel Fuse 功能描述:FUSE

MRF5

制造商:Ferraz Shawmut 功能描述:

MRF50

制造商:Ferraz Shawmut 功能描述:

MRF500

制造商:Ferraz Shawmut 功能描述:

MRF5003

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:N-CHANNEL BROADBAND RF POWER FET